【华科计算机组成原理 】 存储器设计实验

发布于 2021-05-13 17:16 ,所属分类:计算机学习资料大全

华中科技大学-计算机组成原理

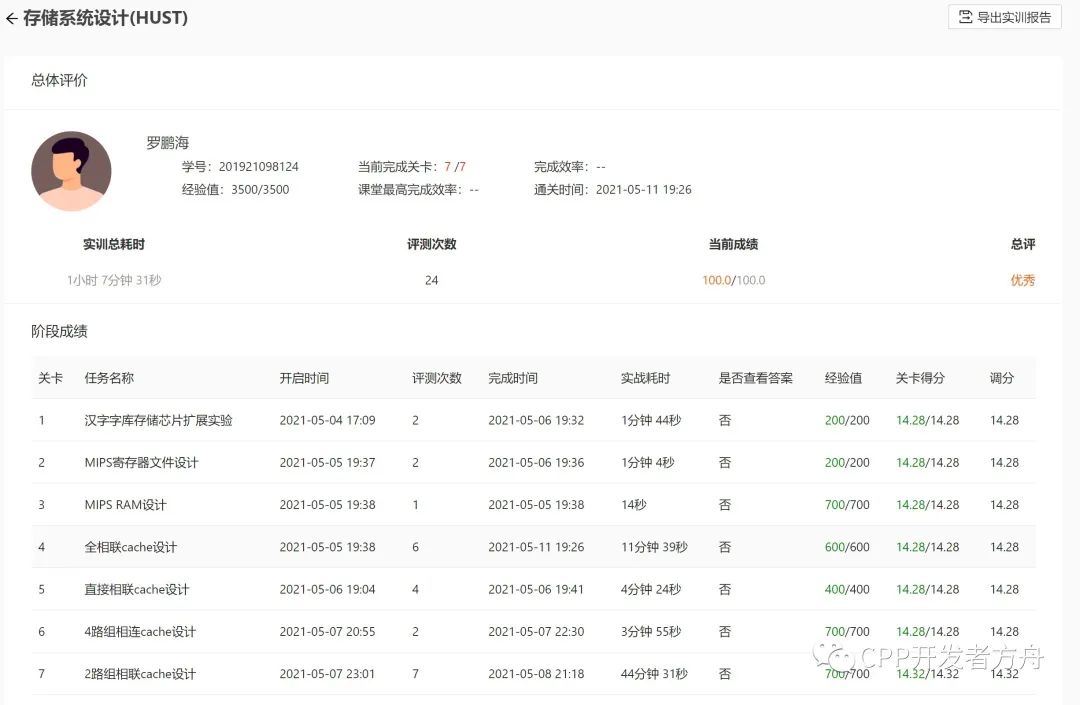

实验二 存储系统设计

-存储系统设计-

下载实验包:storage.circ(全部通关)

https://pan.baidu.com/s/1CeEEkGvGmeXpshEytBJvkA

提取码:8wq7

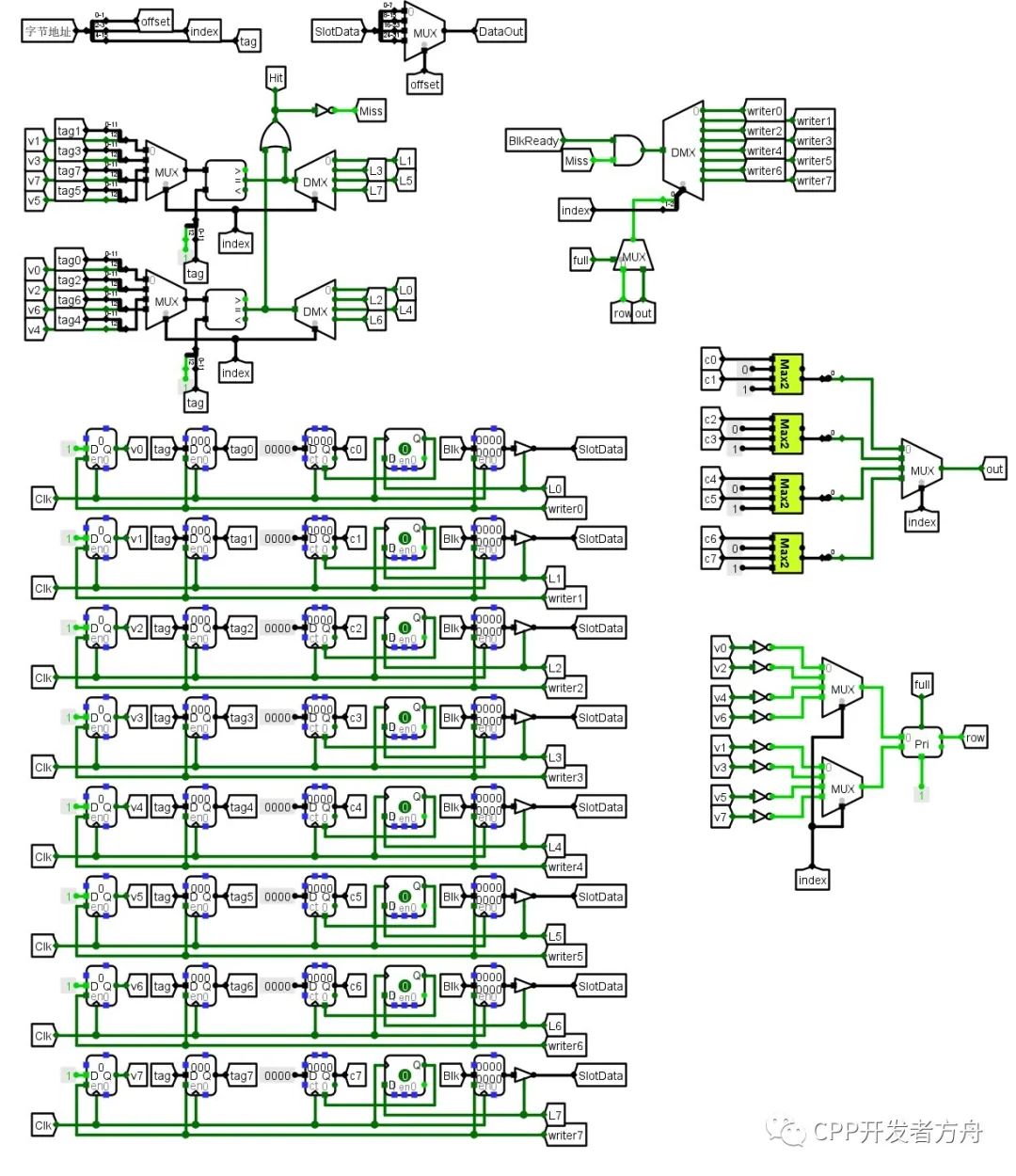

本实训项目帮助大家理解计算机中重要部件—存储器,要求同学们掌握存储扩展的基本方法,能设计 MIPS 寄存器堆、MIPS RAM 存储器。能够利用所学习的 cache 的基本原理设计直接相联、全相联,组相联映射的硬件 cache。

实验目的

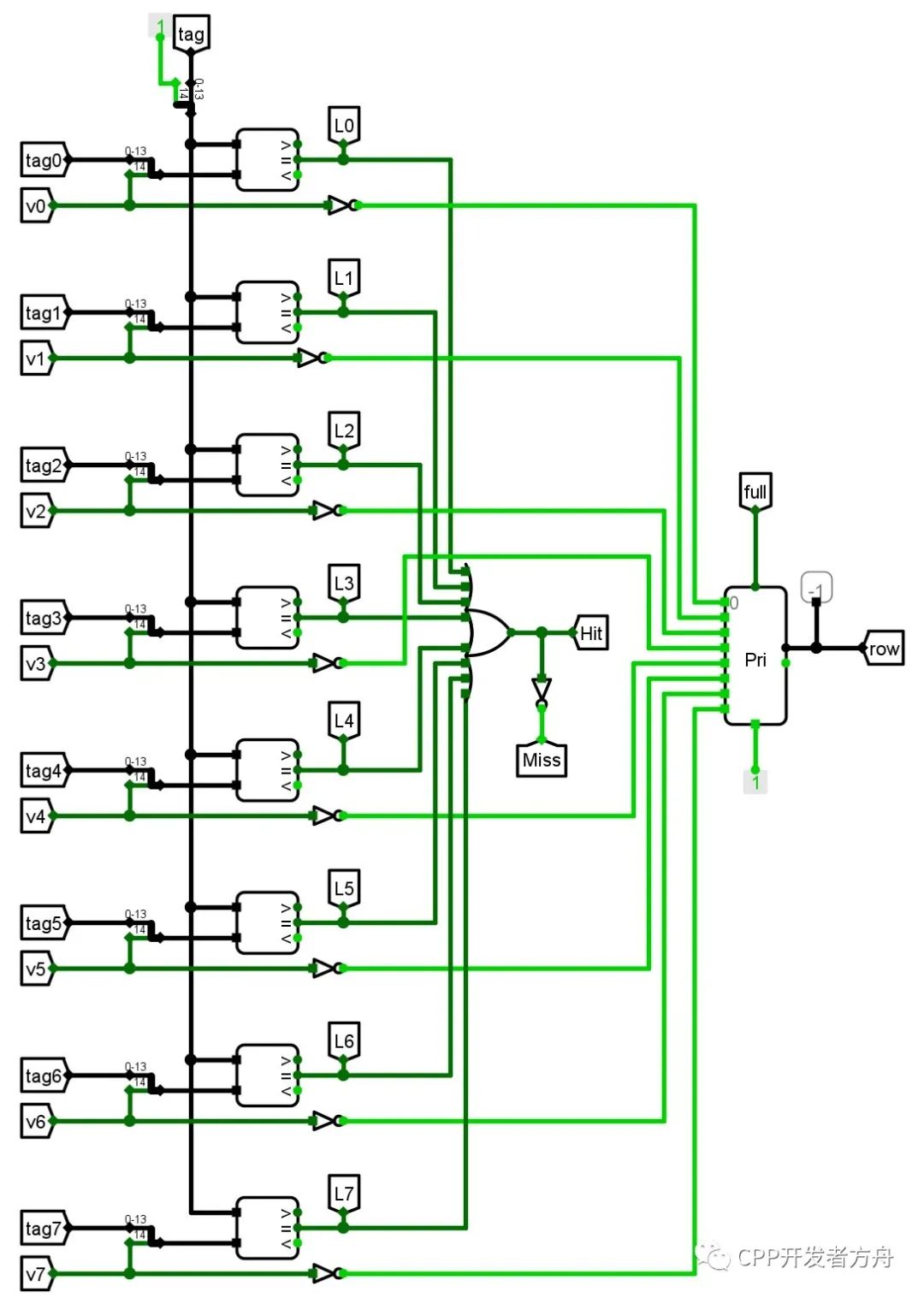

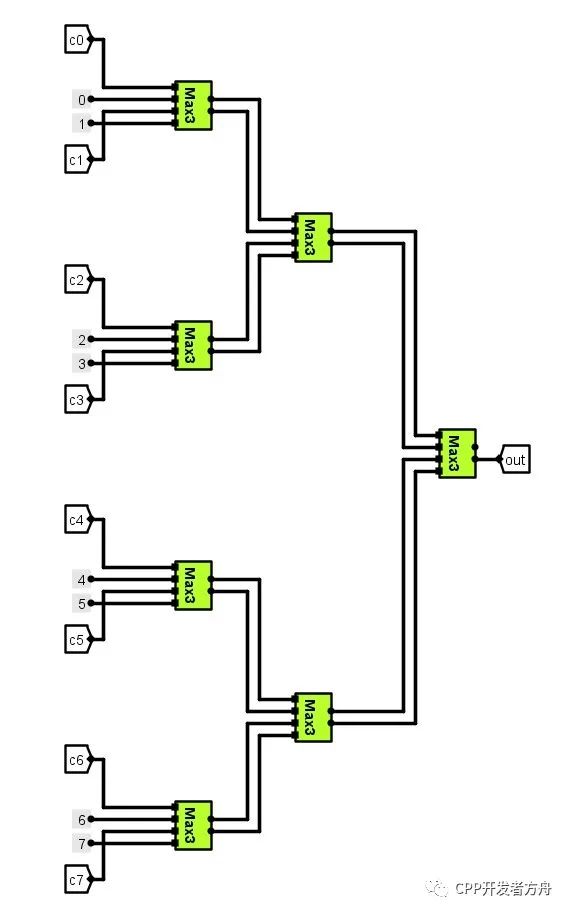

学生掌握 cache 实现的三个关键技术:数据查找,地址映射,替换算法,熟悉译码器,多路选择器,寄存器的使用,能根据不同的映射策略在 Logisim 平台中用数字逻辑电路实现 cache 机制

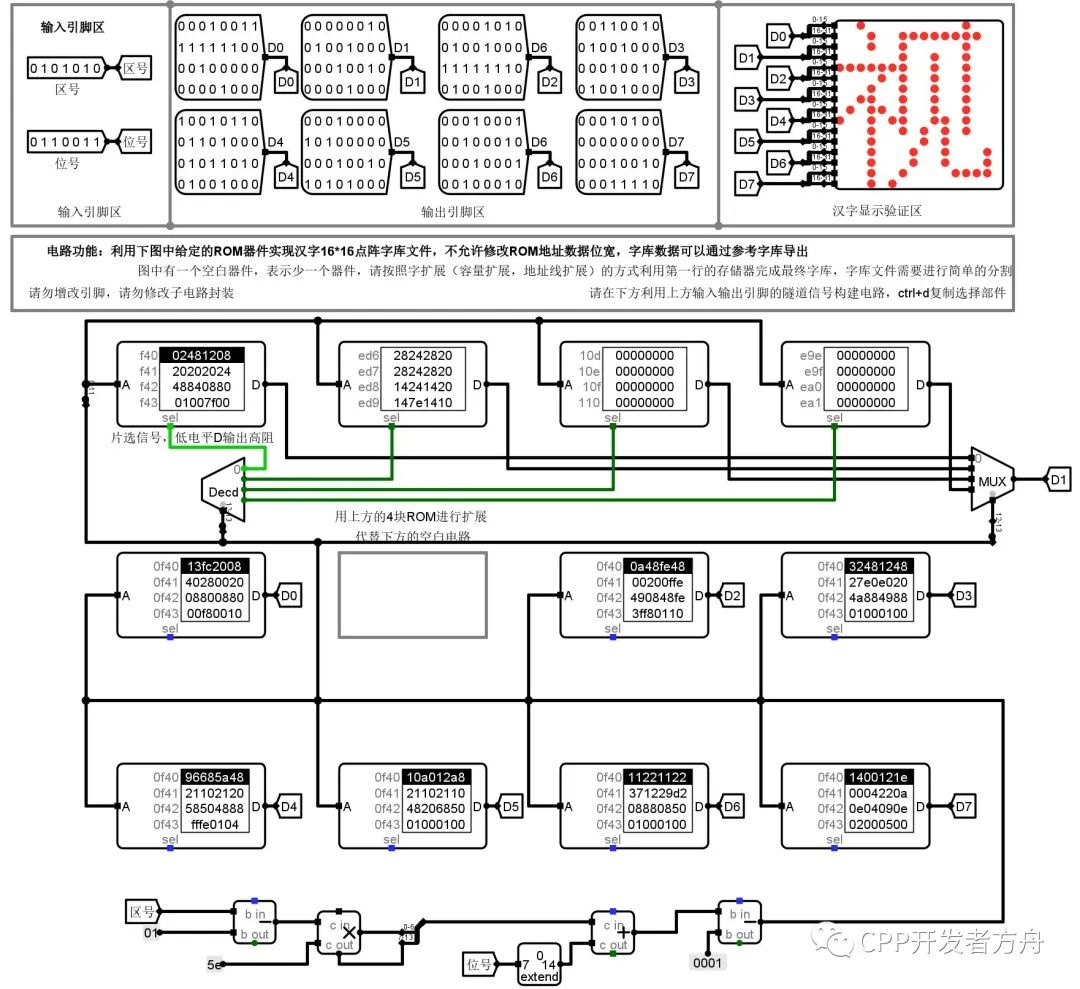

第1关:汉字字库存储芯片扩展实验

测试电路:

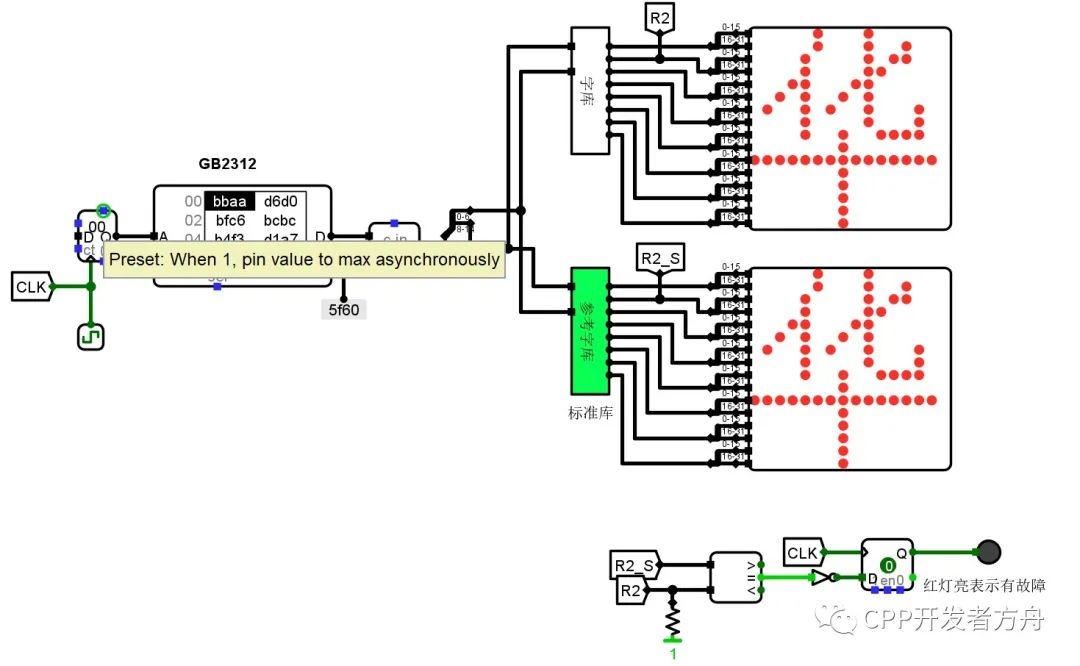

2. MIPS寄存器文件设计

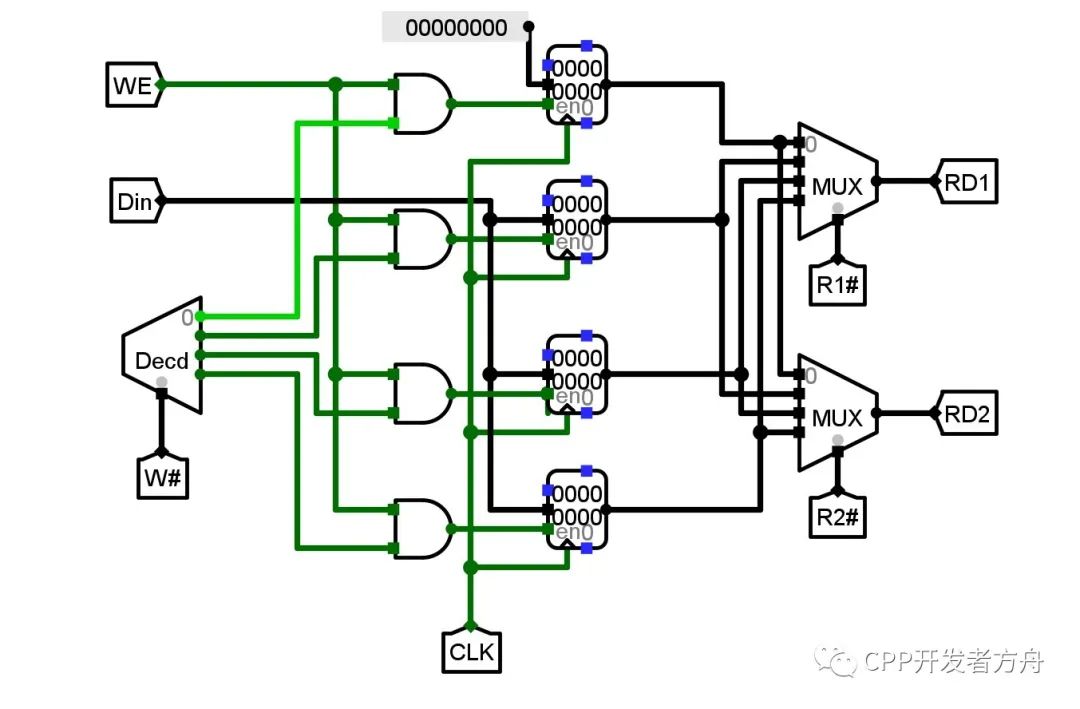

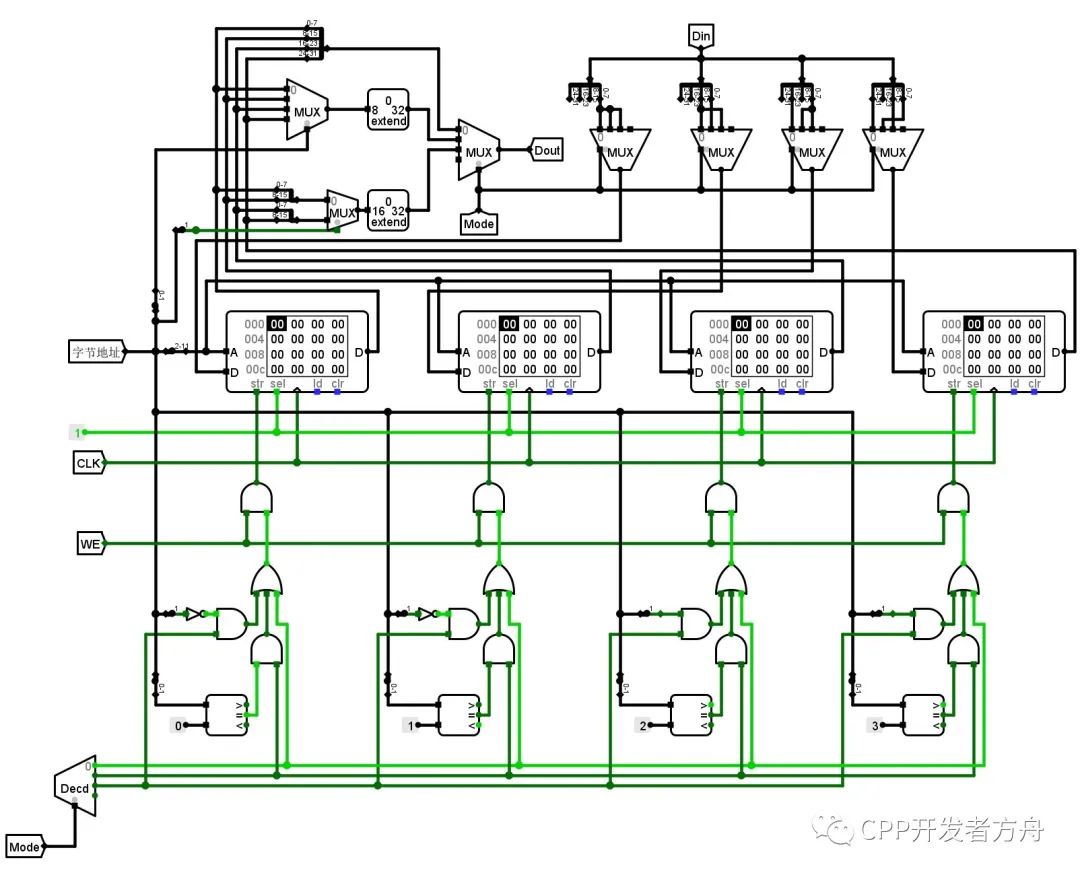

第3关:MIPS RAM设计

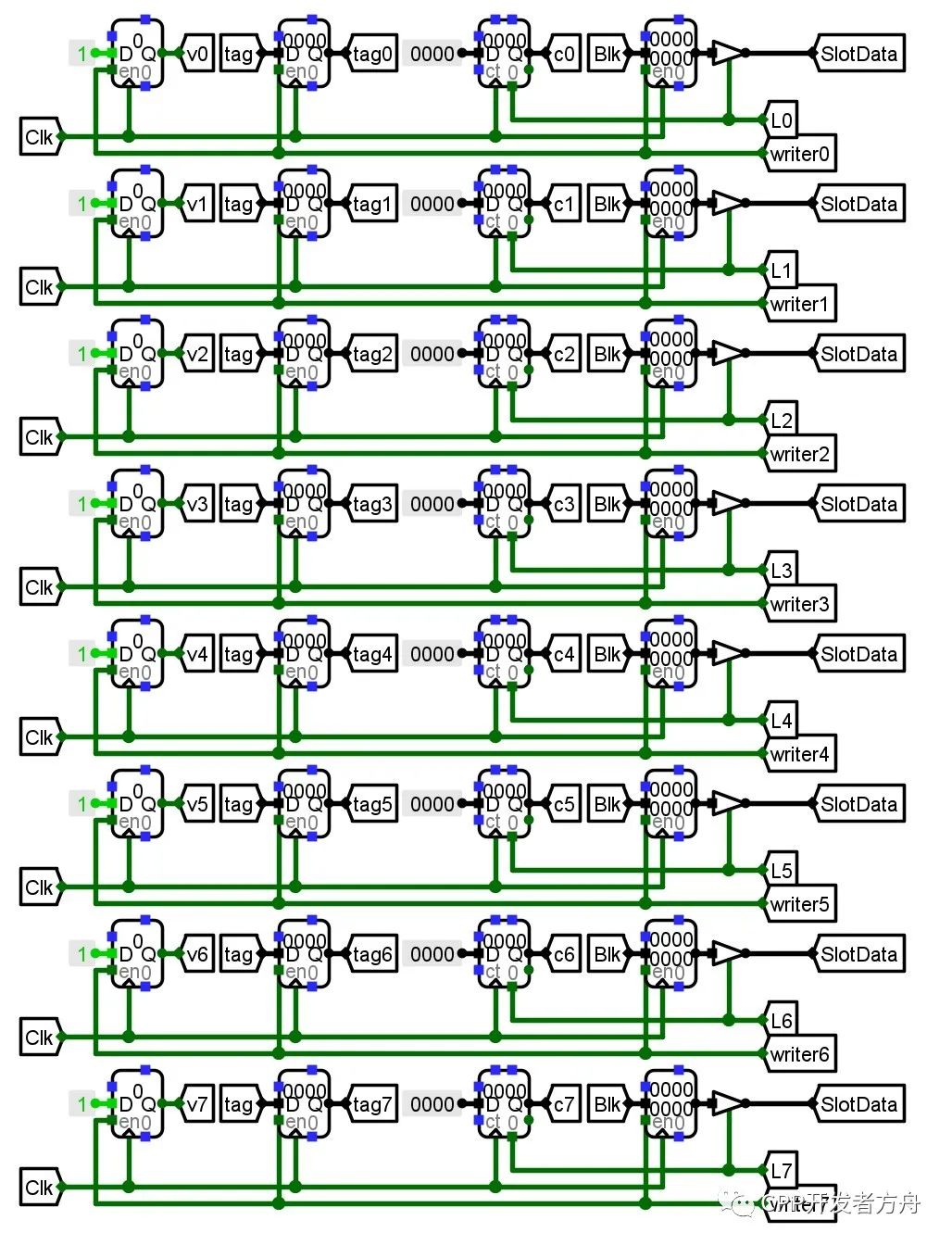

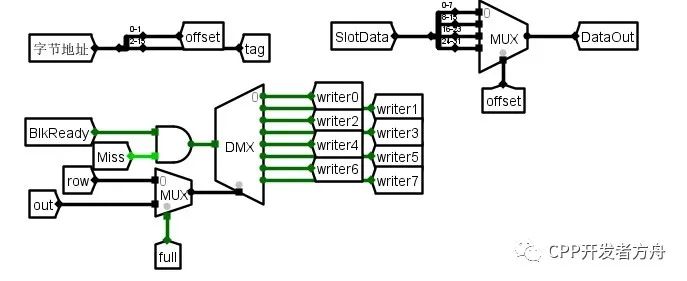

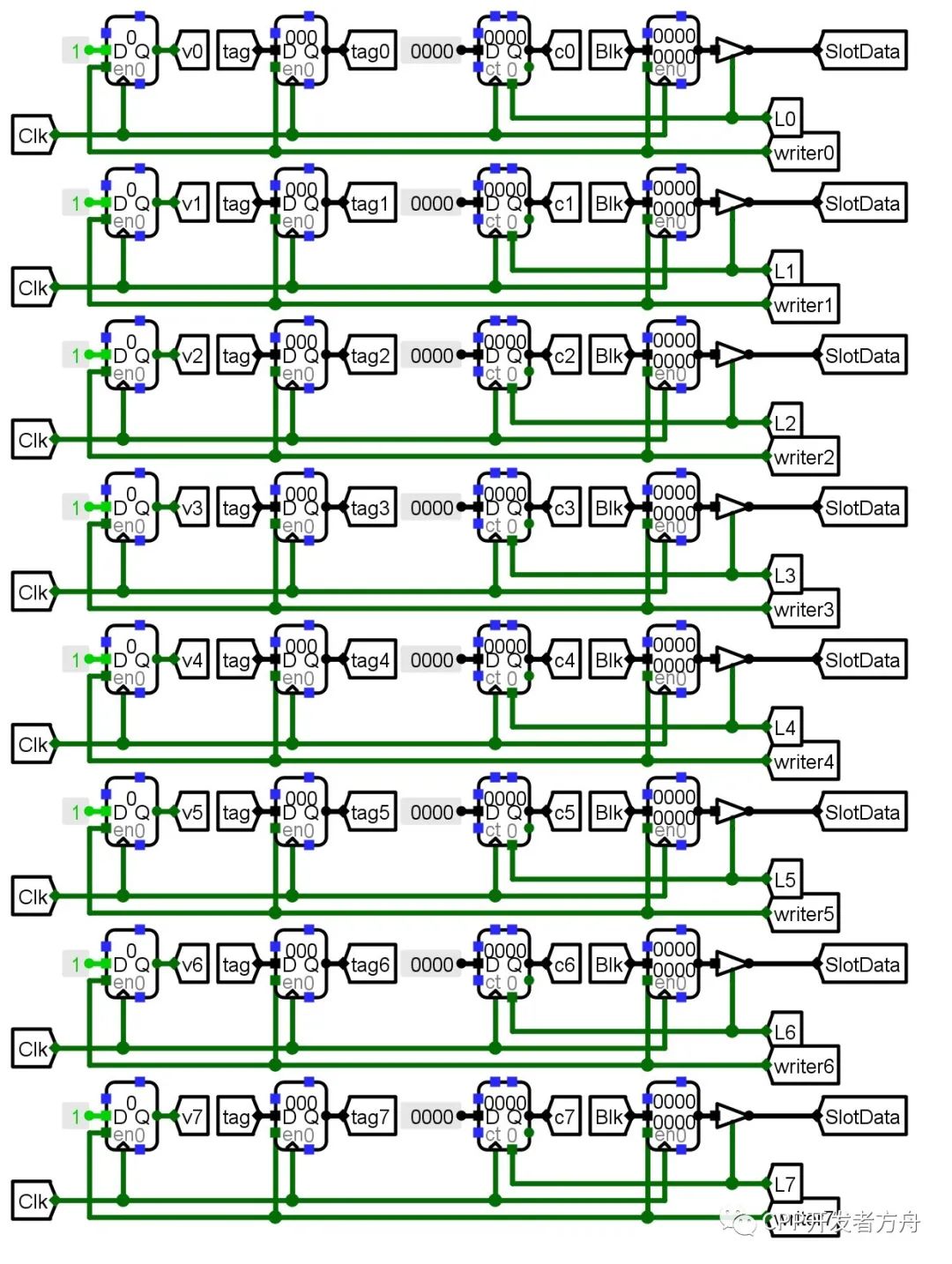

第4关:全相联cache设计

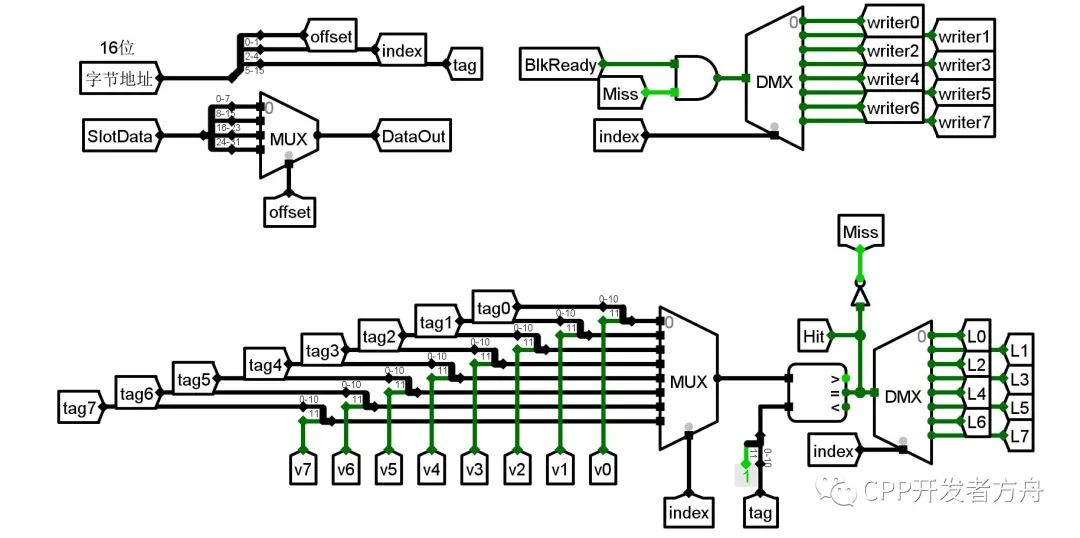

第5关:直接相联cache设计

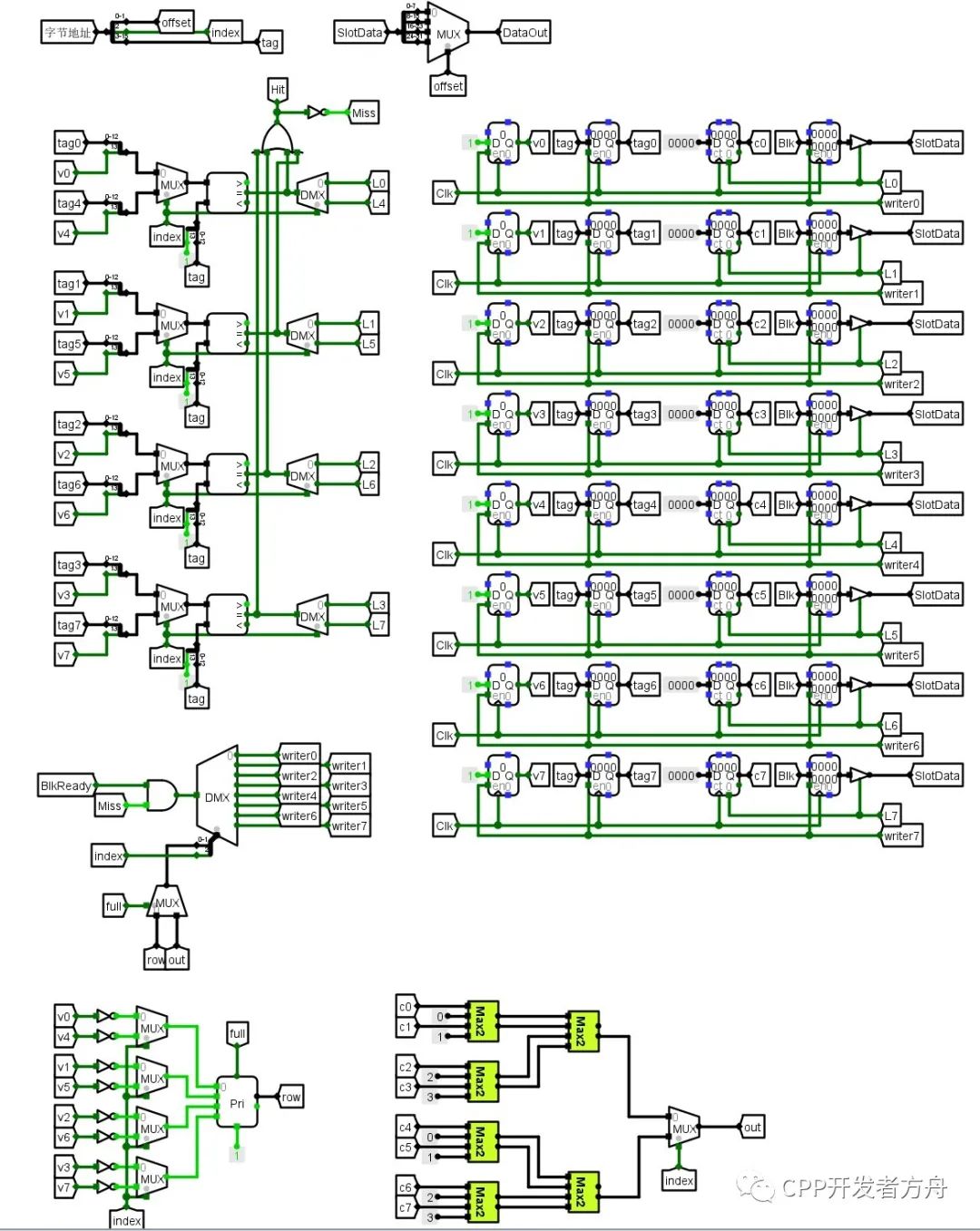

第6关:4路组相连cache设计

第7关:2路组相连cache设计

谭志虎:

清零信号用D触发器串接一下就可以过滤毛刺,另外D触发器默认触发方式是高电平触发,改成上跳沿触发才能过滤毛刺

清零中的毛刺问题解决:清零动作改成同步清零,具体可以增加一个D触发器,将清零信号接输入,输出接异步清零,另外D触发器时钟触发方式请修改为上跳沿。

排版 | ByteCat

平台 | 头哥平台

![[C语言] 吉林大学 计算机专业 视频教程 编译原理 67集](https://static.kouhao8.com/sucaidashi/xkbb/1f6d128bfe58fd0d848dee7933222abc.jpg?x-oss-process=image/format,webp/resize,w_88/crop,w_88,h_88,g_nw)

![[其他] 吉林大学 计算机专业 视频教程 微机原理及汇编语言 85集](https://static.kouhao8.com/sucaidashi/xkbb/1cc3e5b351adb12a294253ccf786c7f1.jpg?x-oss-process=image/format,webp/resize,w_88/crop,w_88,h_88,g_nw)

![[等级考试] 计算机二级视频教程 全套 公共基础知识+计算机基础知识+office 3件套视频教程](https://static.kouhao8.com/sucaidashi/xkbb/fea5cb739d2bba7fc6b8cc9510c598c7.jpg?x-oss-process=image/format,webp/resize,w_88/crop,w_88,h_88,g_nw)

![[CCNA RS] 微软资深MVP韩立刚老师的计算机网络原理及思科CCNA视频课程1-4章](https://static.kouhao8.com/sucaidashi/xkbb/054a9b2a201d79341ed0a312c27c237e.jpg?x-oss-process=image/format,webp/resize,w_88/crop,w_88,h_88,g_nw)

相关资源